- 全部

- 默认排序

答:第一步,选中整个原理图的根目录,然后执行菜单Tools-Annotate,如图3-56所示,进行原理图选项的编辑;图3-56 原理图进行编译示意图第二步,然后对器件的位号进行复位的操作。在弹出的原理图编译界面中,如图3-57所示,在Action选项中,现将原理图本身已经存在的位号全部复位,点击Reset Part References to “?”,则全部的位号则变成的问号,可参照图3-57所示。 图3-57 原理图编位号复位设置示意图第三步,把所有的位号进

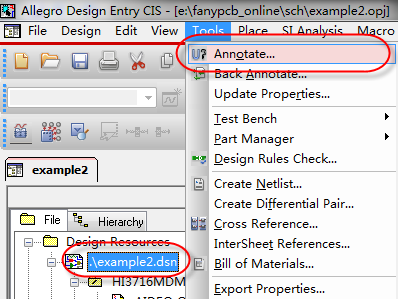

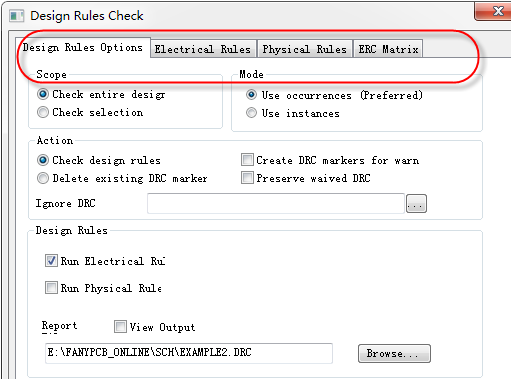

答:第一步,选择原理图的根目录,然后执行菜单Tools-Design Rules Check,进行设计规则的检查,如图3-61所示; 图3-61 进行DRC检查示意图第二步,弹出的DRC检测界面中,有4项的参数可以设置,可以依次进行选择,如图3-62所示,Design Rules Options为检查的参数设置,Electrical Rules为电气规则检查参数设置,Physical Rules为物理规则检查参数设置,ERC Matrix为DRC矩阵设置是否报DRC。 图3-

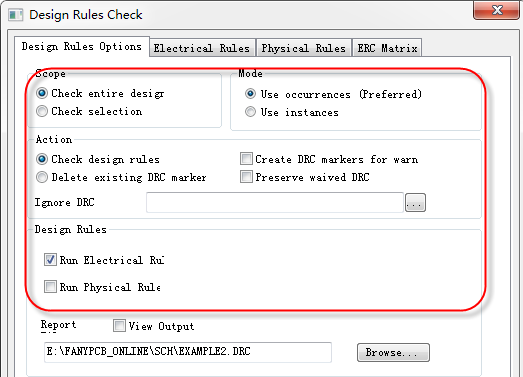

答:orcad进行DRC检测时,如图3-63所示,需要对参数进行设置,每个参数的含义如下所示: 图3-63 DRC参数上设置示意图Check entire design:DRC检查整个原理图;Check Selection:DRC检查选择的部分电路;Use occurrences:选择所有事件进行检查;Use instances(preferred):使用当前实体(建议)。所谓实体是指放在绘图页内的元件符号,而事件指的是在绘图页内同一实体出现多次的实体电路。例如,在复杂层次

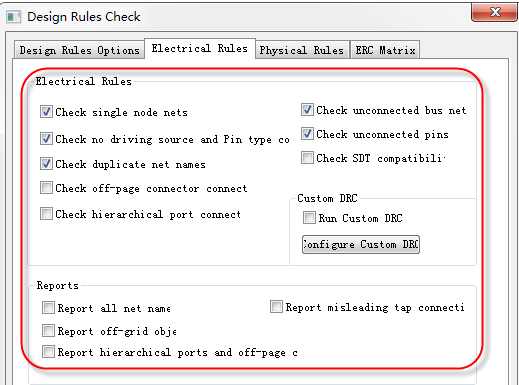

答:orcad进行电气DRC检测时,如图3-64所示,需要对检查的每一项参数进行设置,每个参数的含义如下所示: 图3-64 电气规则检查参数设置示意图Check single node nets:检查设计中的单端网络;Check no driving source and pin type…:检查器件属性无源管脚与有源管脚的连接是否正确;Check duplicate net name :检查重复的网络名称;Check off-page connector connect:检测分页图纸

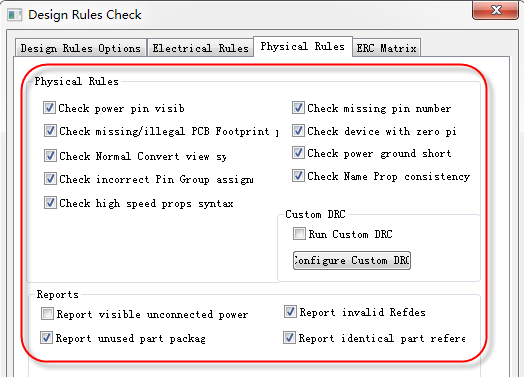

答:orcad进行物理DRC检测时,如图3-65所示,需要对检查的每一项参数进行设置,每个参数的含义如下所示: 图3-65 物理规则检查参数设置示意图Check power pin visible:检测电源属性的管脚是否显示了管脚名称与编号;Check missing/illegal PCB Footprint:检测封装名称是否填写。是否含有非法字符;Check Normal convert view system:检测一个部件的正常视图上的pin号是否与转换视图上的pin号不同;Ch

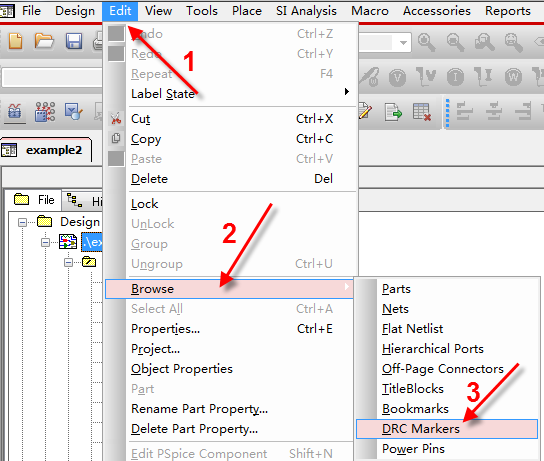

答:对原理图文件进行DRC检测以后,按照设置的DRC检测的选项,会在原理图中留下DRC的标记,对于分页的原理图来说,每一页每一页的去查看DRC的标记,比较繁琐,这里可以运用Browse功能,查看所有的DRC,操作方法如下:第一步,选中原理图的根目录,执行菜单Edit→Browse功能,然后选择DRC Marks,进行DRC标记的查看,如图3-66所示: 图3-66 浏览DRC Marks设置示意图第二步,执行命令以后,如图3-67所示,DRC ERROE显示的是错误的类型说明,DRC

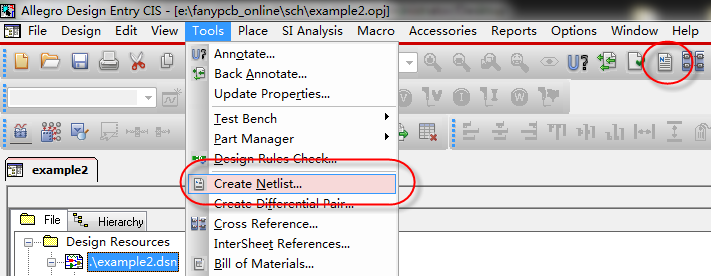

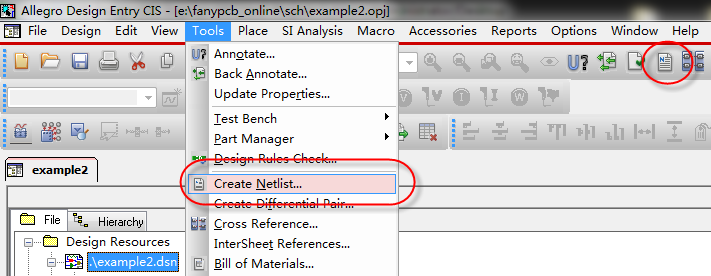

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-68所示; 图3-68 产生网表示意图第二步,弹出的Creat Netlist界面中,选择的是PCB Editor,产生Allegro的第一方网表,如图3-69所示; 图3-69 Allegro第一方网表参数设置示意图第三步,输入Allegro第一方网表需要注意下面几个

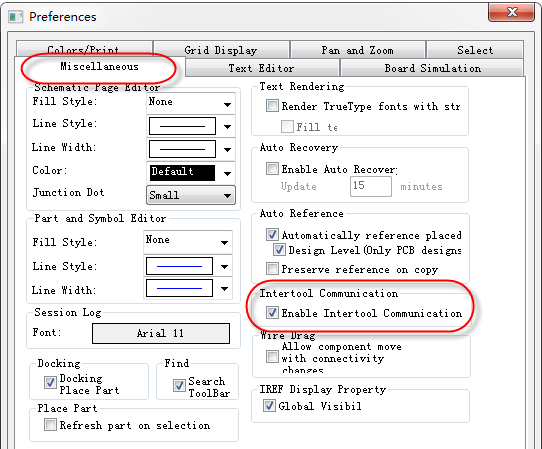

答:orcad与Cadence Allegro的交互式操作需要满足以下两个要求才可以实现:Orcad输出的是Allegro的第一方的网表,Allegro导入的是第一方网表,输出的具体方法见第3.35问;Orcad软件需要勾选以下选项,才可以实现交互式的操作,执行Options→Preference选项,选择Miscellaneous选项,如图3-71所示,在Intertoos Communication选项中,勾上下面的选项,才可以进行交互式操作; 图3-71 交互式操作示

答:使用Orcad软件进行输出Allegro第一方网表时,弹出如图3-72所示的界面,这个是表示原理图有错误,不满足Allegro软件的要求,不能输出网表, 图3-72 输出Allegro网表报错示意图在输出Allegro第一方网表弹出这个界面,我们需要找到如图3-72所示的netlist.log这个文件,原理图中存在的错误在这有详细的描述,这个文件一般存储于输出网表的那个文件夹下,用写字本文件打开此文件,如图3-73所示,将列表中所列的错误一一解决掉,即可输出网表文件了。

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-74所示; 图3-74 输出网表示意图第二步,弹出的输出网表界面中选择Other选项,来输出第三方网表,如图3-75所示,在Formatters栏中选择orTelesis.dll选项,上面的Part Value栏需要用PCB Footprint来代替,不然会产生错误;

扫码关注

扫码关注